Improving Developer Productivity

We eliminate the manual grind of EDA tools through agentic automation. Building the intelligence layer that breaks the silicon design bottleneck.

We eliminate the manual grind of EDA tools through agentic automation. Building the intelligence layer that breaks the silicon design bottleneck.

We are building an end-to-end framework where specialized agents collaborate across the semiconductor stack.

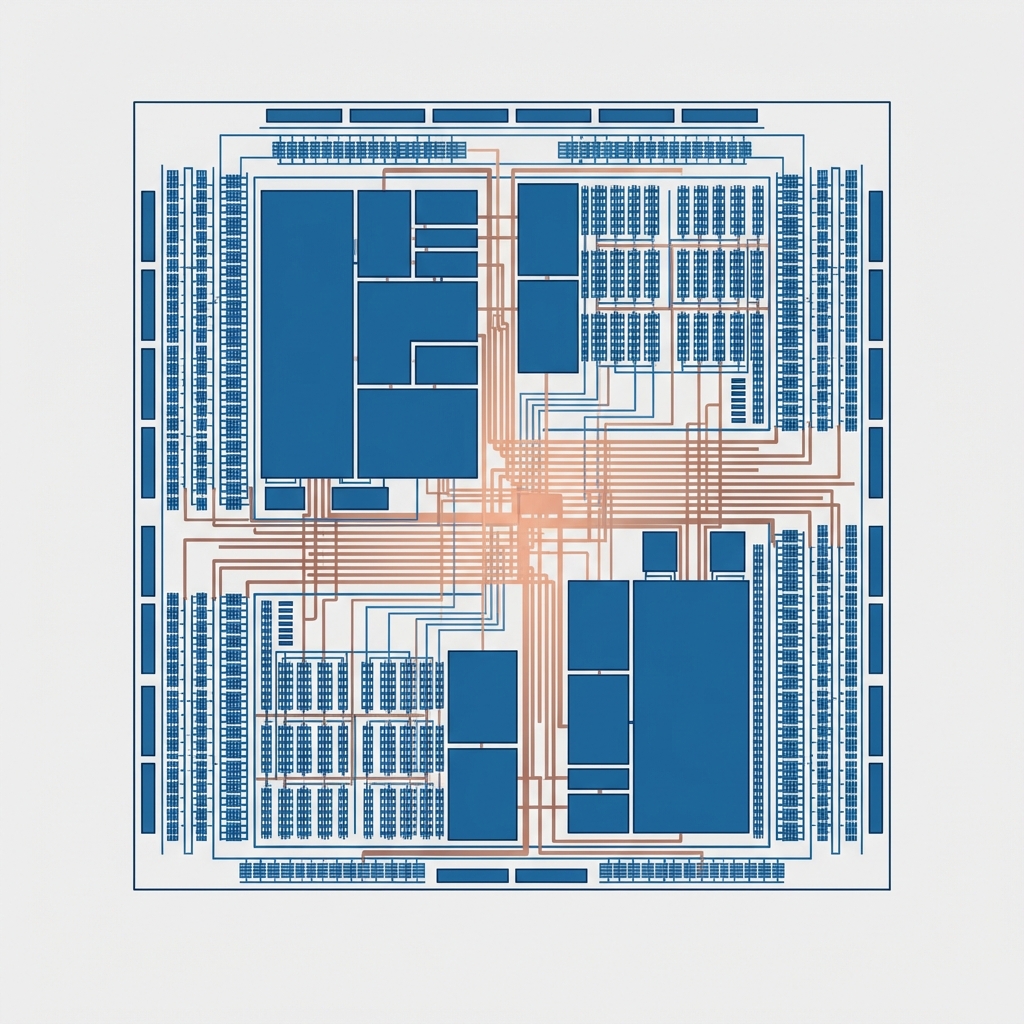

Automating the path to GDSII. We employ intelligent agents for macro placement, pin assignment, and floorplanning optimization to minimize congestion and resolve timing violations early in the flow.

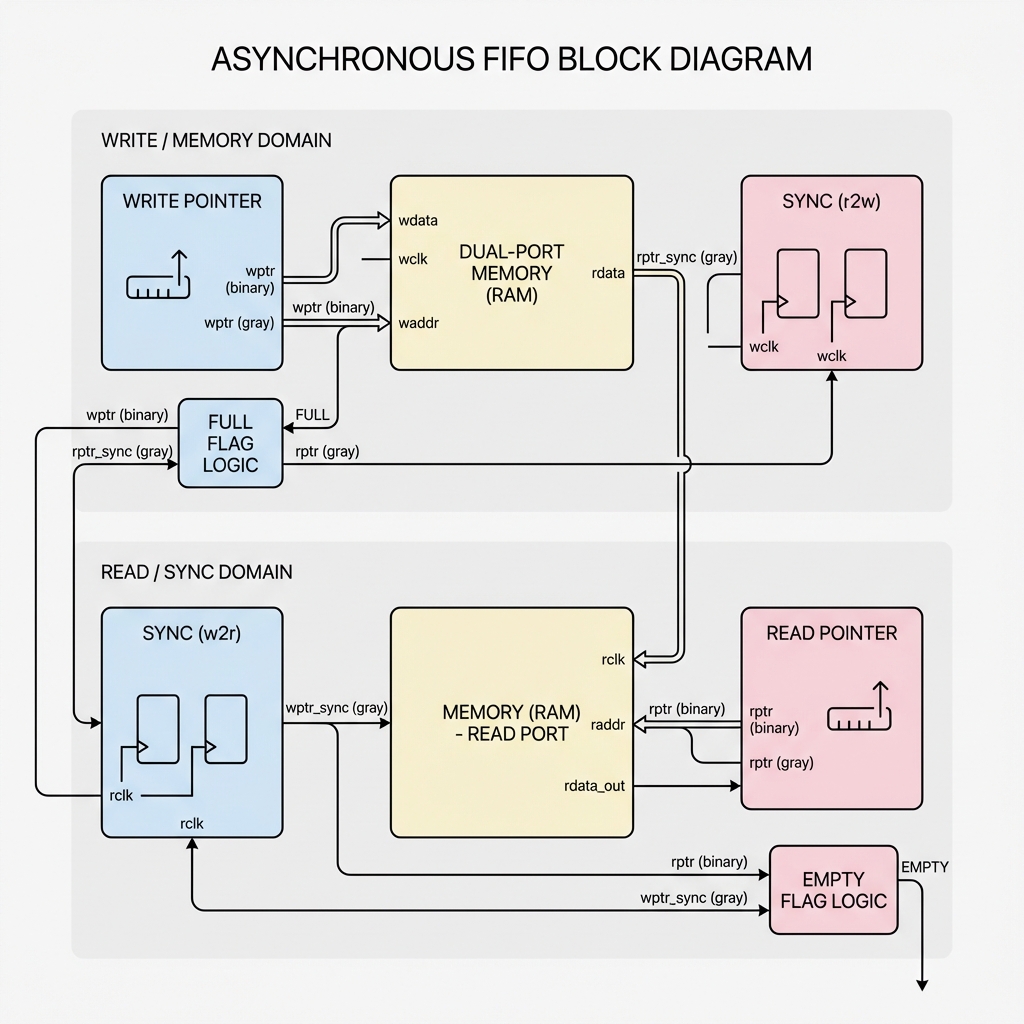

Gain instant clarity into your design. Our semantic engine instantly generates interactive, high-fidelity block diagrams from Verilog, allowing effortless navigation through complex hierarchies.

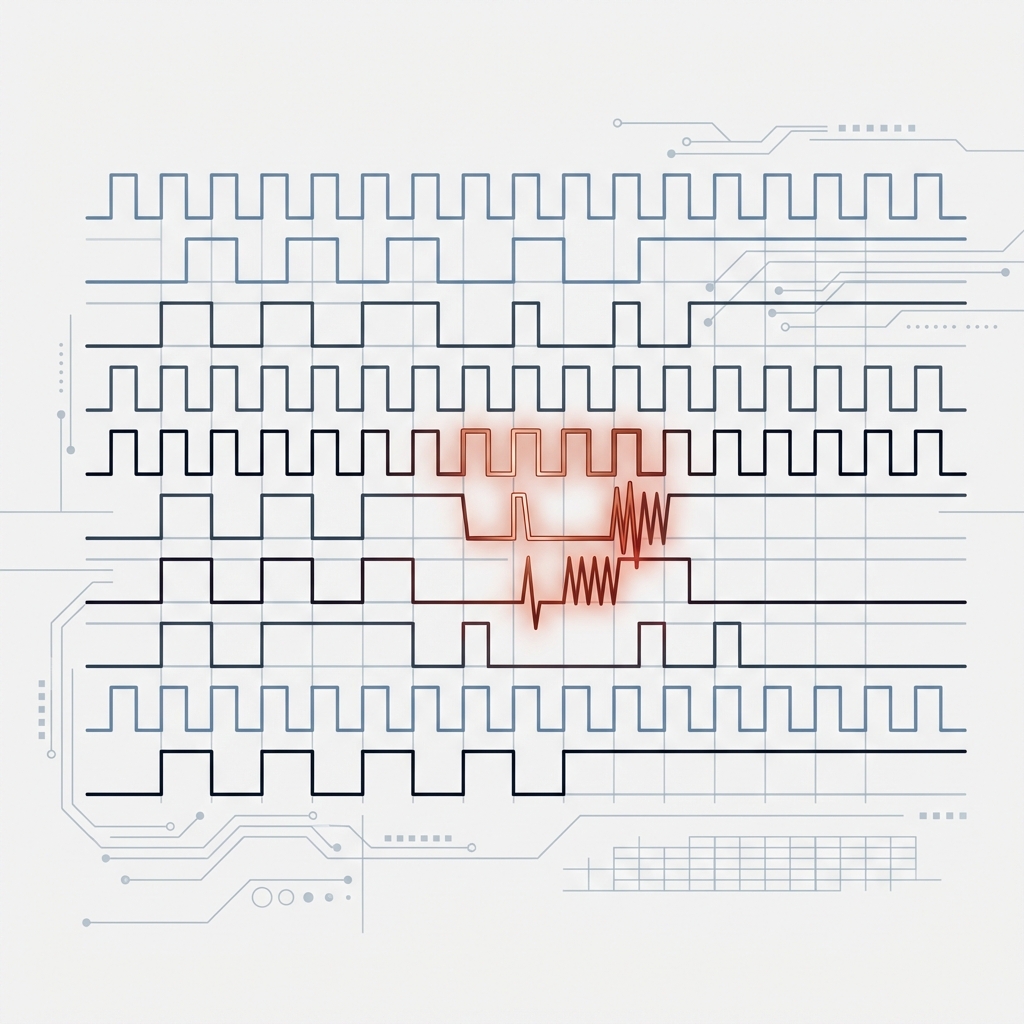

Slashing debug time by 10x. Our agents autonomously parse massive simulation logs and waveform datasets (VCD/FSDB) to pinpoint root causes of failures and suggest RTL fixes in real-time.

Establishing the foundation for the next generation of silicon design.

The semantic engine for hardware engineers. Used by thousands to visualize and inspect complex RTL hierarchies with AI-driven depth.

Our broader agentic framework is in early access. Partnering with industry leaders to deploy Architect, RTL, and Verification agents in production.

RESERVE EARLY ACCESSIntegrate ArchGen intelligence into your existing Verilog workflows in minutes.

Install the RTLViz semantic engine via Python package manager.

pip install rtlvizAutomatically configure your IDE for the semantic server.

rtlviz setupAfter setup, ask your AI assistant on side panel:

"Use rtlviz MCP to generate a diagram for the in <path to code>"